Abstract

Ternary is the new binary. Classical computing favors 0's and 1's mainly because of practical engineering. Using three states - ternary - is mathematically proven to be the optimal discrete signal encoding on the lowest hardware level. And it paves the way for even higher radices, closer to Nature's billion year solution to computing: the brain.

Three states will allow computers to think beyond black and white and introduce new fundamental logical constructs to reason with. Imagine having an extra letter in the alphabet and the new words that can be made. Compared to binary, data will be more compressed, faster processed, have less latency in communication and use less energy.

USN is Norway's premier university where ternary computing and multiple valued logic (MVL) is actively taught and researched for over a decade.

Keywords: ternary computing , post-binary technology , USN

Principal Investigators

Introduction

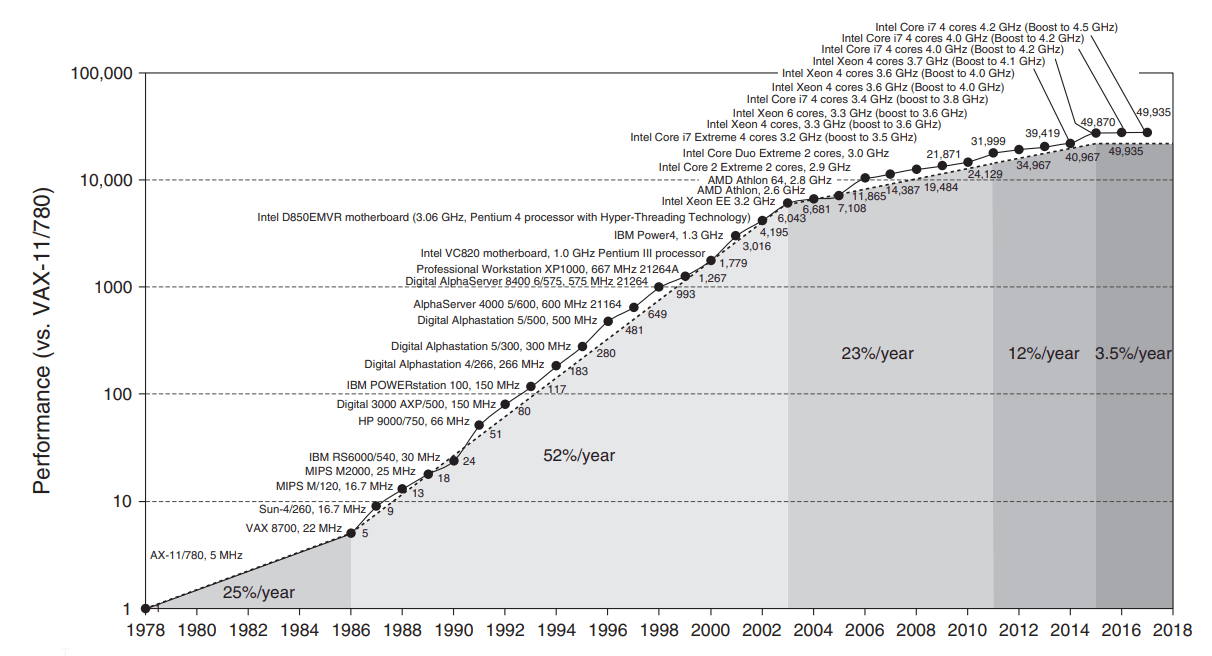

Moore's Law [Moore, 1965] has been a guiding principle for the semiconductor industry, enabling 40 years of exponential growth of compute power. Although the limit of transitor density has not plateaud with Gate-All-Around transistors replacing finFETs, its growth curve has declined significantly. Dennard scaling law ended already in 2006. Now, the economy of scale is not to minituarize IC's but stick to older nodes. A complete paradigm shift is needed for computing that scales the next 40 years.

By expanding the number of stable states from two to three, the same amount of computations can be done with less transistors per unit die area thus generating less heat and leakage current. Complexity is reduced as less wiring between logical circuits is needed. Most importantly, the enabling technology is not - like quantum computing - in the far future, but is already commercially available. Modern multi-level-cell (MLC) SSD's don't store one bit per cell, but trap a growing number of discrete charges. With memristors and neuromorphic computing, the classical Von Neumann bottleneck can be broken using extremely low power. Carbon nanotube transistors feature high electron mobility, can be 3 ångström in diameter (some atoms are 1 Å!) and their diameter functions as a variable voltage threshold. Mass production of these multi-valued devices could enable new scaling laws that are directly related to smaller noise margins and higher information density per mm^3.

Figure 1. Historical compute performance. End of Dennard scaling and dusk of Moore's Law (Patterson & Hennessy, 2021. Copyright Elsevier)

Figure 2. The first modern ternary computer: the Setun (source: unknown)

Just like electrical cars were invented before the combustion engine cars in the late 1800's, ternary computers have been invented long before the classical computer chips we now use daily. In 1840 Thomas Fowler build the first mechanical ternary computer to aid his treasury work [Glusker, 2005] and [Shilov, 2009]. Later, in 1958 the first modern ternary computer was build by Russian engineer Brusenzov and his team [Hunger, 2007] at some scale. It did not become popular due to technology readiness, it lacked ternary storage for instance as it "simply" discarded the fourth state. Nevertheless this complex system was claimed to be more reliable, faster and more affordable compared to its binary counterpart. To this day, ternary computing and multiple valued logic receives stable international interest as recorded in the proceedings of the oldest conference on MVL, ISMVL.

With modern technology in place, ternary computers are ready to disrupt virtually every sector. History has proven that sectors like the automotive industry, food, defense and space, finance and healtcare all benefit from smaller, more energy efficient and more powerful chips. This website will link old and new research from both our research group and fellow researchers in the field to make ternary computing a reality. The world is is not binary, it is analog.

Results

Beyond CMOS: Ternary and Mixed Radix CNTFET Circuit design, Simulation and Verification (IEEE ISCAS '22)

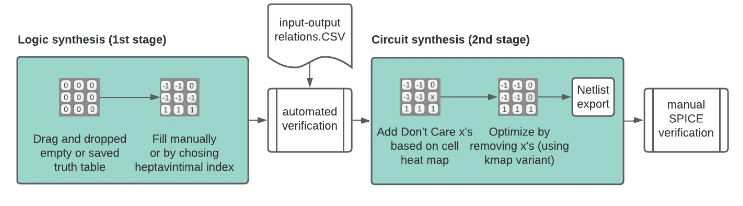

Workflow for MVL circuits using the Mixed Radix Circuit Synthesizer EDA tool

For three-valued or ternary computing to be an alternative for binary, new multiple valued logic (MVL) electronic design automation (EDA) tools are needed. In this article we present a novel MVL logic synthesis tool to generate binary, ternary and hybrid (mixed radix) circuits using carbon nanotube FETs (CNTFETs). The web-based open source EDA tool aids in design, simulation and verification aspects including a direct netlist export to HSPICE. We demonstrate a fundamental building block of a balanced ternary computer using the tool, a ternary D flip-flop. We show that mixed radix design can reduce transistor count.

Try in the browser

Download the source code

Link to paper (proceedings not yet available)

High speed bi-directional binary-ternary interface with CNTFETS (SDPS '21)

Caption

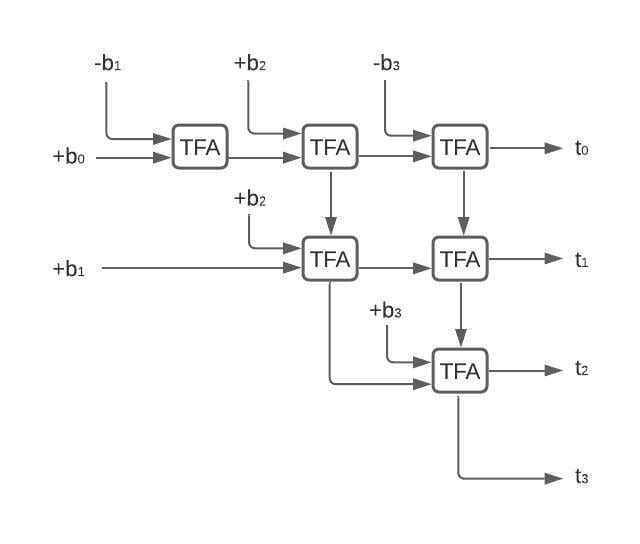

The world is built on binary electronics, thus high speed and bi-directional radix conversion is needed to enable billions of binary devices to co-exist with non-binary ones. In this article we discuss a generic method for conversion between binary and ternary. A CNTFET implementation is given using a balanced ternary full adder. The implementation is simulated using HSPICE 2020 and is made open source. We demonstrate that nibble word conversion speeds of over 25 GB/s with power consumption of 97.8 uW are achievable with 1760 CNTFETs switching at 5 GHz.

Link to paper

Ternary Computing; The Future of IoT? (SDPS '21)

Caption

Ternary logic, in which the number of discrete logic levels are restricted to three, has been a subject to excessive research over several years. In this position paper we discuss advantages and consider the future impact for IoT devices in 7 categories: computational power, communication, compression, comprehension, cyber-security, design complexity and energy consumption.

Link to paper

Post-Binary Robotics: Using Memristors With Ternary States for Robotics Control (IEEE ESTC '20)

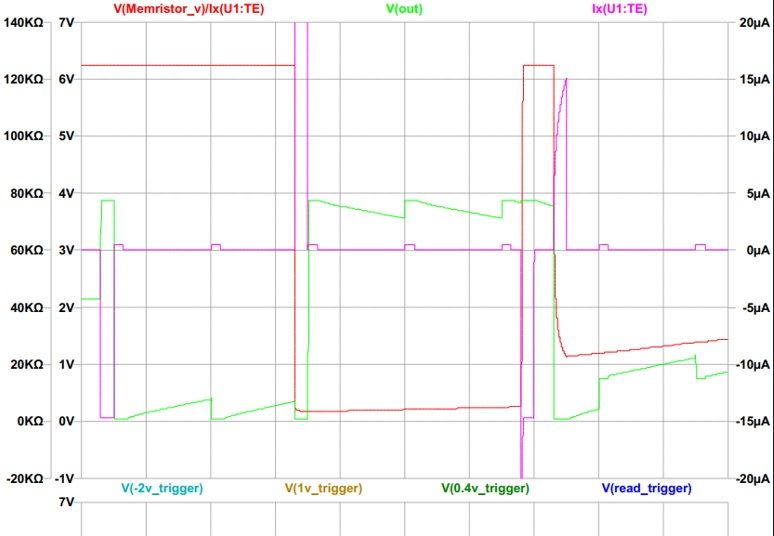

Caption

This paper presents a method to read and write ternary (three-valued) signals on memristors to control a robotic actuator in real-time. The paper is a continuation of earlier work by [Bos et al.,2020] and implements a ternary memory controller for memristors in hardware. This post-binary approach with non-volatile memory is used to program a memristor as a “trit”. The paper contributes to the state-of-the-art in memristor controlled robotics by reporting an entropy gain of log2(3)= 58% information at (20 versus 14)= 43% more component cost compared to binary. This advantage (eg. less wire complexity) increases when multi-trit architectures are considered.

This article demonstrates both an LTspice simulation of the circuit and implementation with source code. The memristor programmer circuit writes a state to the memristor using a pattern of 100us pulses at 3 different amplitudes. The memristor read circuit sends 500 nA pulses and converts these using two reference resistors to three logic levels using an op amp window comparator. An Arduino Mega microcontroller ADC pin converts the analog output to a digital trit. Strenuous effort was made for predictable and replicable applied memristor research in pursuit of a post-binary robotics era. The multiple-valued circuit has safety features to prevent harm to the memristance state, standardized forming of new memristors and programming flexibility by sending patterns of different pulse amounts, pulse width and pulse amplitudes.

Download the source code

Link to paper

Automated synthesis of netlists for ternary-valued n-ary logic functions in CNTFET circuits (SIMS '20)

Caption

This paper is an investigation of automated netlist synthesis for ternary-valued n-ary logic functions, based on a static ternary gate design methodology. We present an open-source C++ implementation, which outputs a ready-to-simulate SPICE subcircuit netlist file for ternary-valued n-ary function circuits. A circuit schematic of the 3-operand carry is demonstrated as synthesized by the netlist generator.

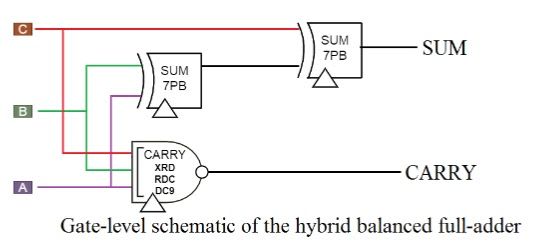

We investigate a holistic (non-compound) approach to designing balanced full-adders by using 3-operand functions as compared to a traditional 2-operand compound design methodology. Three gate-level design approaches (compound, non-compound and hybrid) for the balanced full-adder have been simulated in HSPICE and are compared to each other and the state-of-the-art with simulation results.

Furthermore, we propose to standardize the ternary functions by indexing them. This indexing system allows for the convenience of referencing any possible logic function with no ambiguity. This indexing is necessary as most ternary functions do not have semantic names (e.g. AND, OR) and the amount of unique 3-valued functions grows exponentially with higher arity.

Download the source code

Link to paper

uMemristorToolbox: Open source framework to control memristors in Unity for ternary applications (IEEE ISMVL '20)

Caption

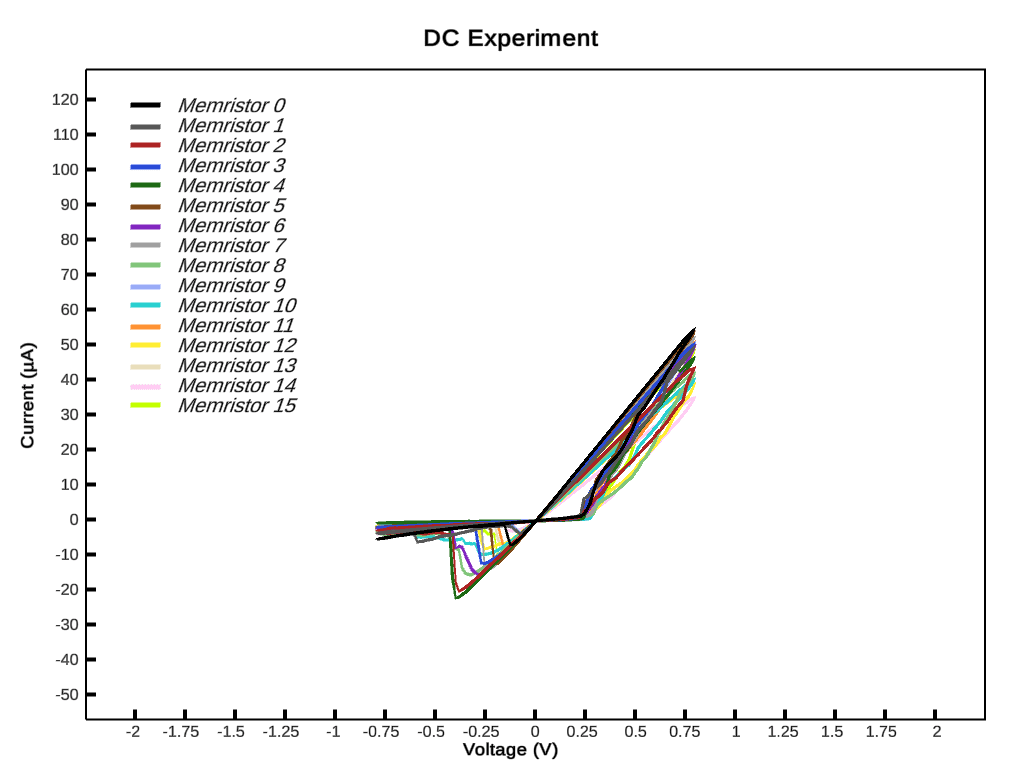

This paper presents uMemristorToolbox, a novel open source framework that reads and writes non-volatile ternary states to memristors. The Unity (C#) framework is a port of the open source Java project Memristor-Discovery and adds a closed-loop ternary memory controller to enable both PC and real-time embedded ternary applications. We validate the closed-loop ternary memory controller in an embedded system case study with 16 M+SDC Tungsten dopant memristors. We measure an average switching speed of 3 Hz, worst case energy usage of 1 µW per switch, 0.03% random write error and no decay in (non-volatile) state retention after 15 minutes. We conclude with observations and open questions when working with memristors for ternary applications.

Download the source code

Link to paper

References

Bos et al., 2020. uMemristorToolbox: Open source framework to control memristors in Unity for ternary applications. In: 2020 IEEE 50th International Symposium on Multiple-Valued Logic (ISMVL)

Bos et al., 2020. Post-Binary Robotics: Using Memristors With Ternary States for Robotics Control. In: 2020 IEEE 8th Electronics System-Integration Technology Conference (ESTC)

Bos et al., 2021. High speed bi-directional binary-ternary interface with CNTFETS. In: 2021 Proceedings of the Society for Design and Process Science (SDPS)

Bos et al., 2022. Beyond CMOS: Ternary and Mixed Radix CNTFET Circuit design, Simulation and Verification. In: 2022 IEEE 55th International Symposium on Circuits and Systems (ISCAS)

Glusker, 2005. http://www.mortati.com/glusker/fowler/index.htm

Gundersen et al., 2021. Ternary Computing; The Future of IoT?. In: 2021 Proceedings of the Society for Design and Process Science (SDPS)

Hunger, 2007. SETUN: An inquiry into the Soviet Ternary Computer, Online exerpt: http://online.fliphtml5.com/beej/trqu/

Risto et al., 2020. Automated synthesis of netlists for ternary-valued n-ary logic functions in CNTFET circuits. Linköping Electronic Conference Proceedings (SIMS)

Shilov, 2009. http://www.computer-museum.ru/precomp/fauler.htm (Google translate)